8’b01001111 << 3 8’b01111000

8’b01001111 <<< 3 8’b01111010

8’b01001111 >> 3 8’b00001001

8’b01001111 >>> 3 8’b11101001

Условный оператор

Условный оператор имеет три операнда, разделенные двумя операторами в

следующем формате:

cond_expr? true_expr: false_expr;

Если условие (cond_expr) вычисляется как «ложное» (false), то в качестве результата

будет использовано выражение false_expr. Если условие «истинно» (true), то будет

использовано выражение true_expr.

Операция объединения (конкатенация)

Операция конкатенации является одной из наиболее удобных и мощных операций в языке Verilog. Суть ее заключается в слиянии нескольких переменных в единое целое, единую переменную, с которой можно производить любые другие операции.

Необходимо отметить два момента: операция конкатенации обладает наивысшим приоритетом по сравнению с любой другой операцией вне символов конкатенации ({}), но операции заключенные внутри фигурных скобок имеют еще больший приоритет (Операции внутри фигурных скобок это недокументированное свойство языка, главное в этом случае, чтобы в результате внутренней операции результат получил определенную разрядность). Вторым моментом является тот факт, что операция конкатенации недопустима с вещественными числами. Синтаксис операции приведен ниже: {<expr_1>, <expr_2>, … <expr_n>};

Операция может содержать несколько повторяющихся элементов, для сокращения записи используется множитель, который указывает сколько раз повторяется данный элемент: {4{w}} эквивалентно {w, w, w, w}

Множитель может быть целой, неотрицатеьной константой или константным

выражением. Также в операции могут использоваться внутренние объединения: {{a, b, c}, {3{d, e}}} эквивалентно {a, b, c, d, e, d, e, d, e}

Результат операции слияния может использоваться в любом случае в качестве операндов или в качестве вектора (переменной) которой присваивается значение. Это широко используется для случаев, когда функция должна вернуть несколько значений.

С целью закрепления знаний языка описания аппаратуры, рассмотрим примеры описания ЦУ на языке Verilog.

Пример создания на САПР Quartus II цифрового устройства с использованием языка описания аппаратуры Verilog

Создадим на САПР Quartus II логический элемент 2И-НЕ с помощью языка описания аппаратуры Verilog. Для этого:

· Выбрать в главном меню "File\New Project Wizard…" ("Файл\Мастер создания проекта…") (рис. 2.33).

Рис. 2.33

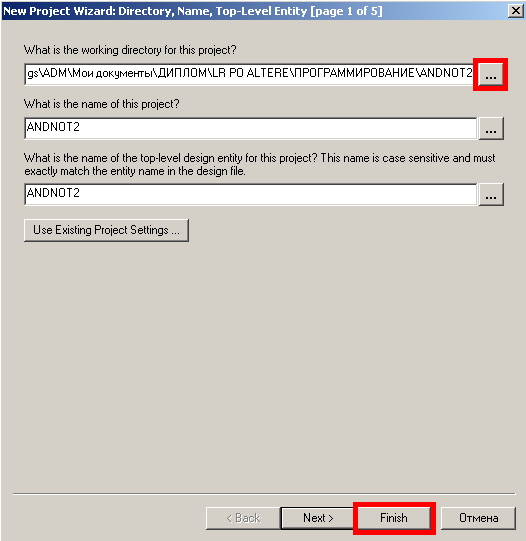

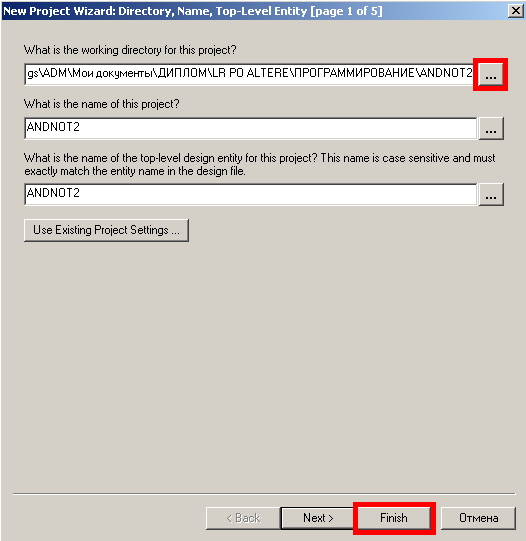

· В появившемся окне "New Project Wizard: Directory, Name, Top-Level Entity [page 1 of 5] " (" Мастер создания проекта: Папка, Имя и Модуль верхнего уровня [страница 1 из 5]") щелкнуть по кнопке с тремя точками у верхнего поля ввода. В новом окне "Select Directory" ("Выбрать папку"), переместившись в желаемое место на диске, создать новую папку для вновь создаваемого проекта под именем, например, "ANDNOT2" и " зайти" в неё (папка необходима, поскольку проект содержит около пятидесяти файлов). После этого щелкнуть по кнопке "Отрыть" окна "Select Directory".

· Возвратиться в окно "New Project Wizard: Directory, Name, Top-Level Entity [page 1 of 5] " и убедиться в том, что в верхнем поле ввода занесен полный маршрут к созданной папке, а именно, во втором поле – имя проекта, которое совпадает с именем папки, и в третьем (нижнем) поле – имя модуля верхнего уровня, совпадающего с именем папки. Щелкнуть по кнопке " Finish" ("Завершение") (рис. 2.34).

Рис. 2.34

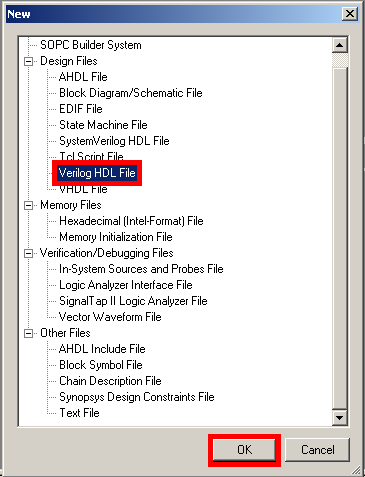

· Выбрать в главном меню "File\New…" ("Файл\Новый") (рис. 2.35).

Рис. 2.35

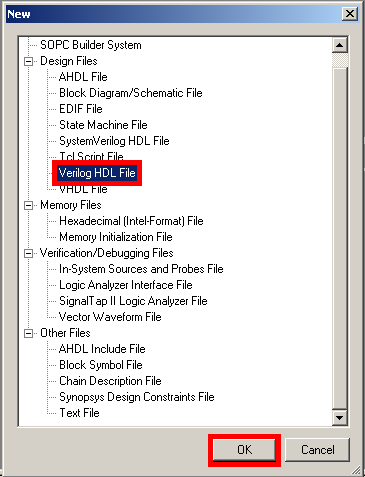

· В появившемся окне " New" на закладке "Device Design File" ("Конструкторские файлы устройств") выбрать строку " Verilog HDL File " ("файл на универсальном языке описания аппаратуры Verilog ") (рис. 2.36). Щелкнуть по кнопке "ОК" в нижней части окна.

Рис. 2.36

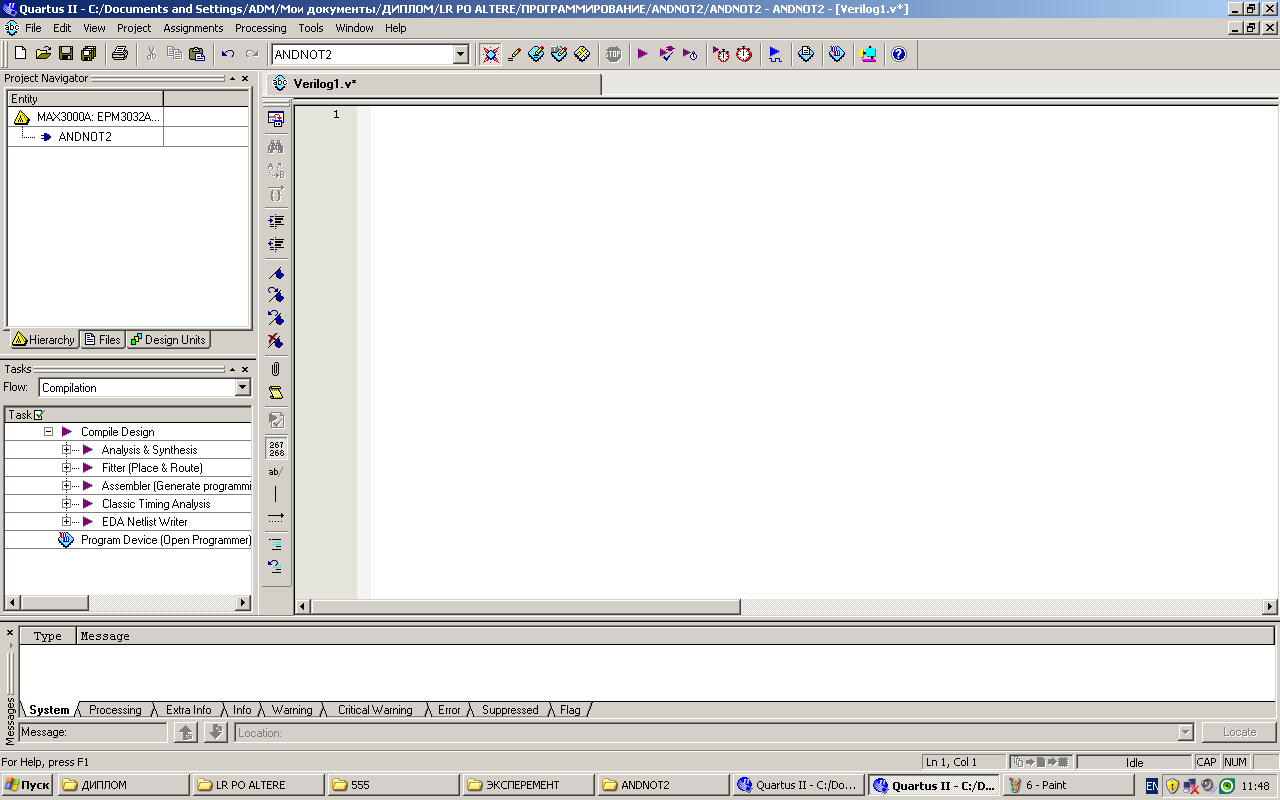

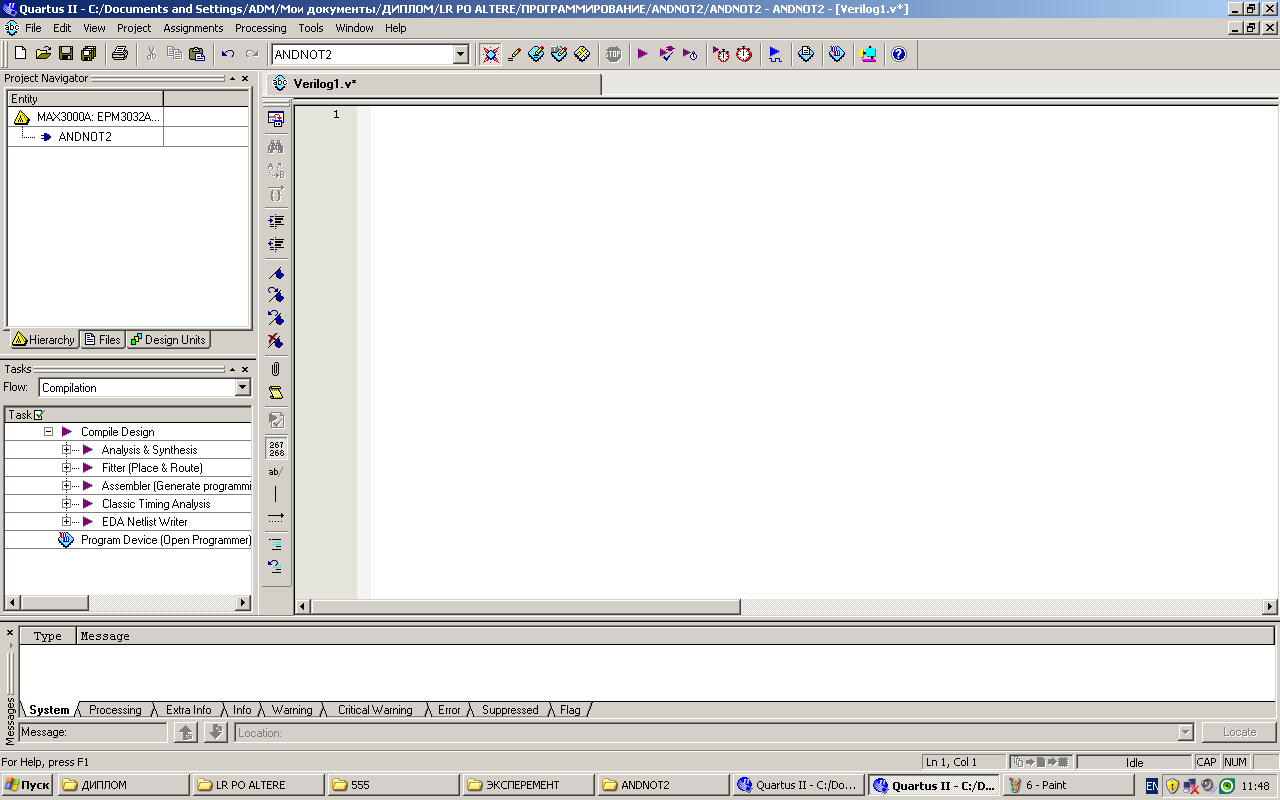

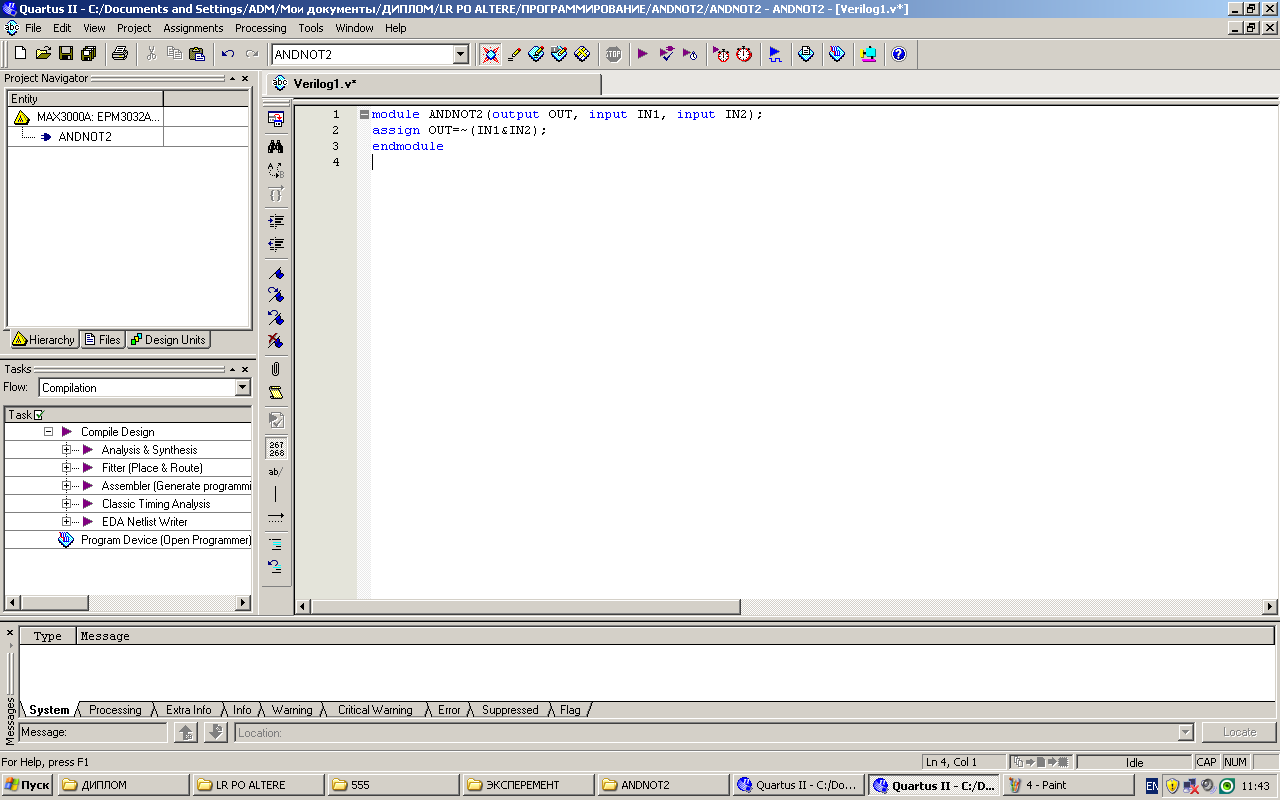

· На рабочем поле приложения появится окно созданного файла с именем в квадратных скобках ["Verilog.v"]. Его расширение ".v" означает, что это " Verilog HDL File ", т.е. файл с языком описания в Verilog (рис. 2.37).

Рис. 2.37

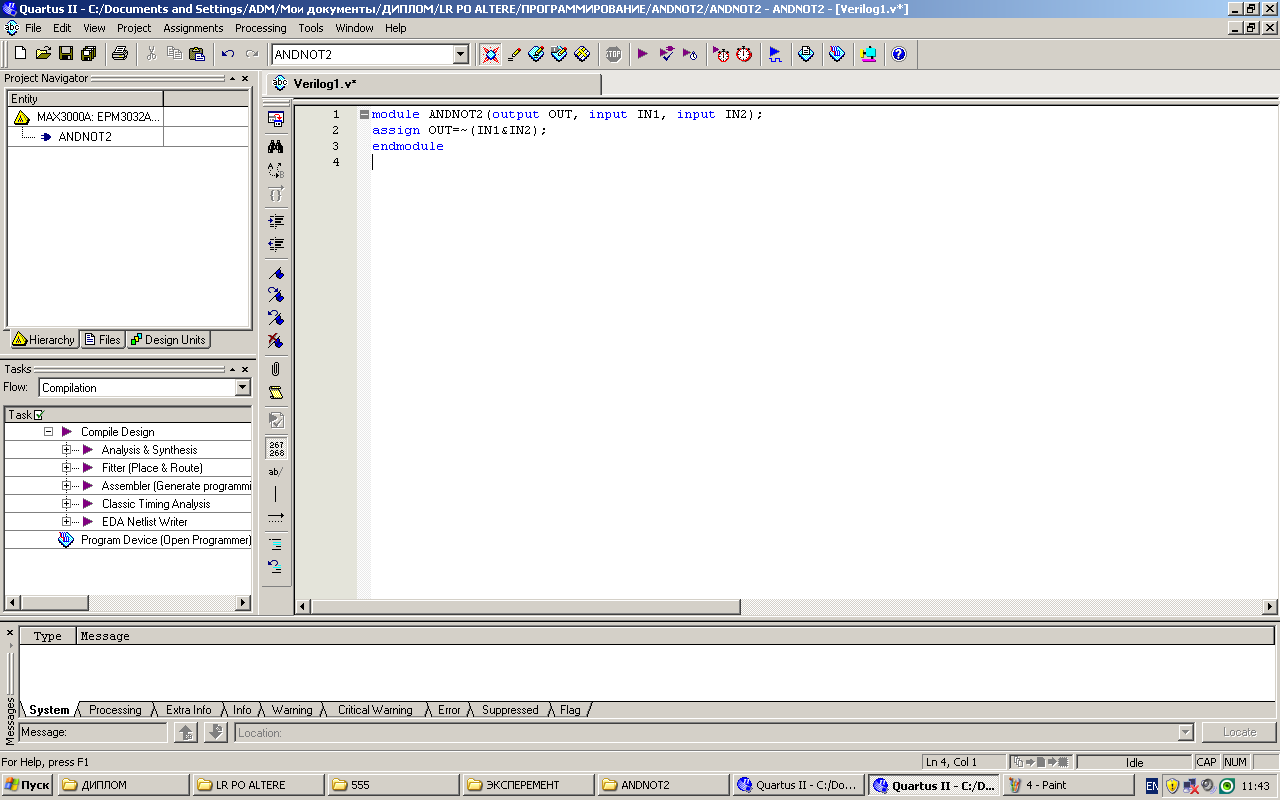

· Описать схему 2И-НЕ в verilog HDL (рис. 2.38):

module ANDNOT2(output OUT, input IN1, input IN2);

assign OUT=~(IN1&IN2);

endmodule

Рис. 2.38

· Выбрать в главном меню "File\Save As" ("Файл\Сохранить с Новым Именем ").

· В появившемся окне "Сохранить как" будет предложено сохранить файл с именем проекта с расширением. v. Следует принять предложение и щелкнуть по кнопке "Сохранить".

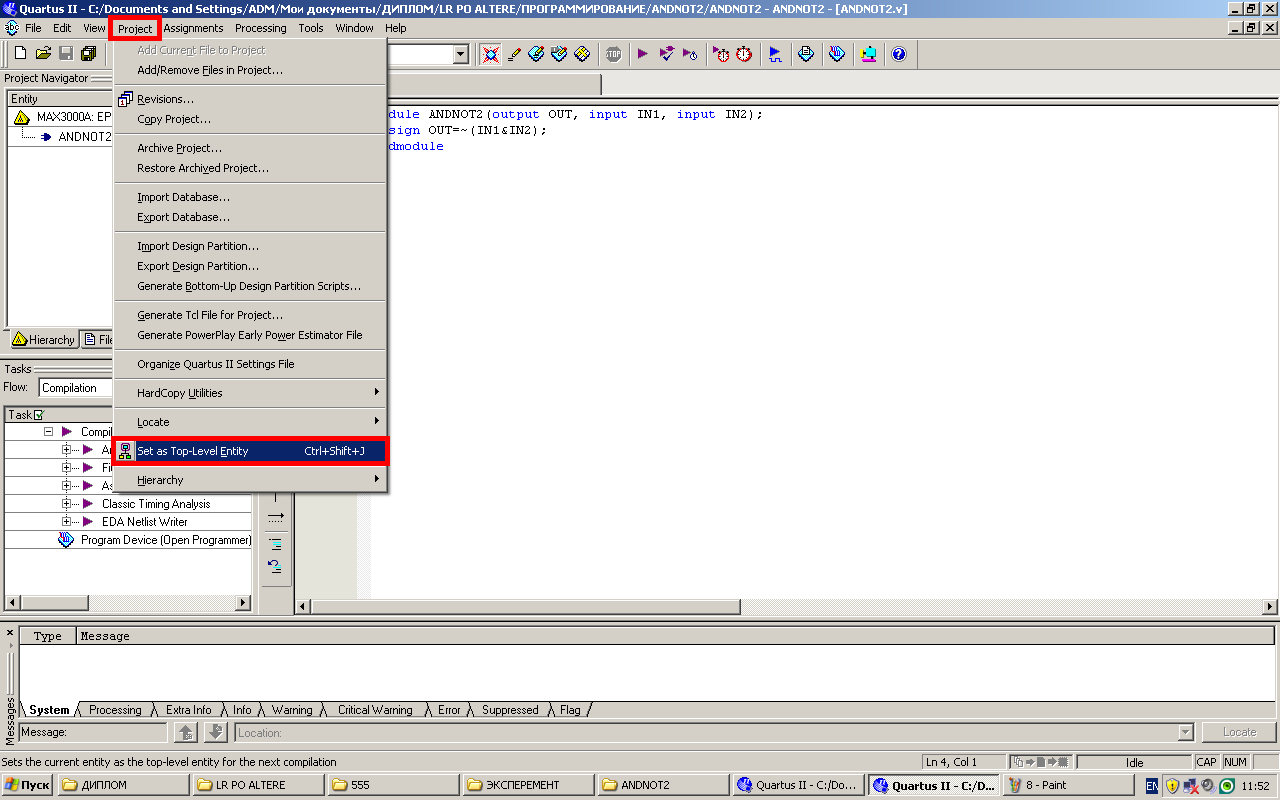

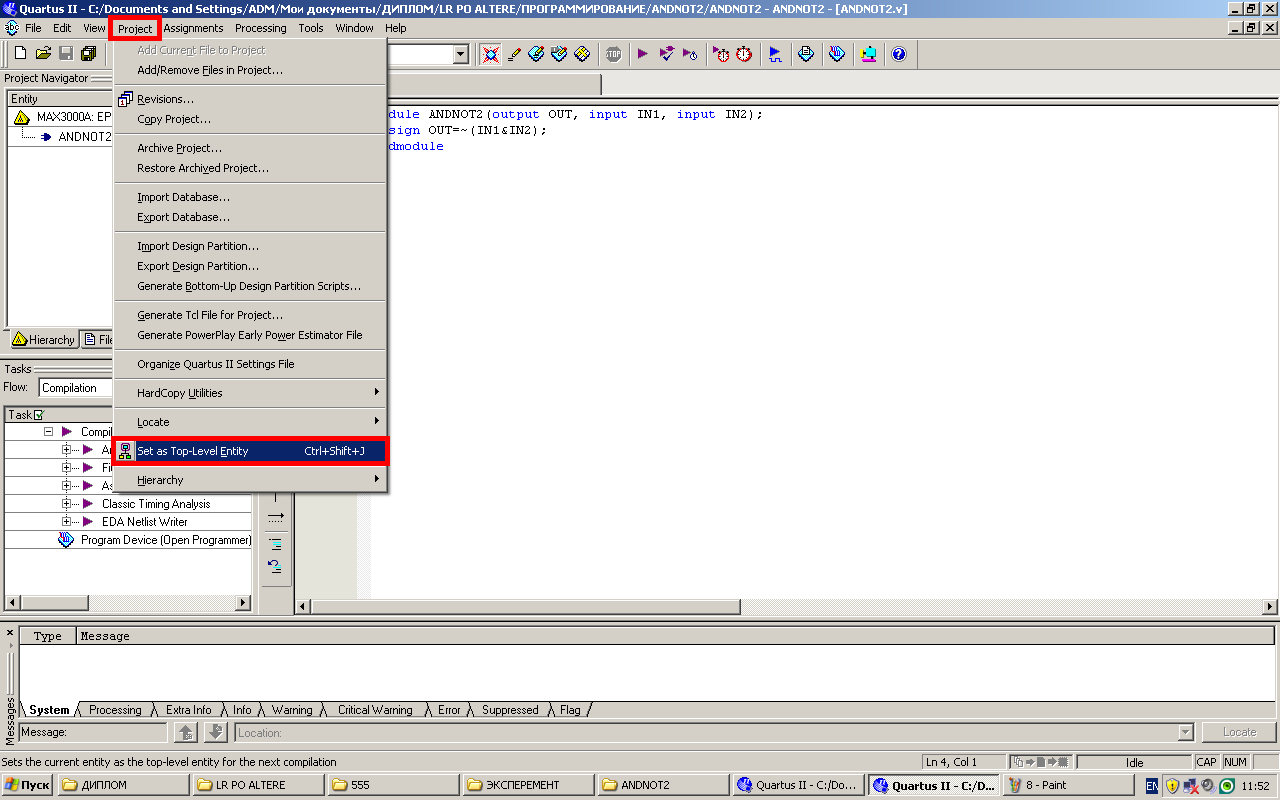

· Сделаем текущий файл главным файлом проекта, для этого выбираем в главном меню Project/Set As Top Level Entity (рис. 2.39).

Рис. 2.39

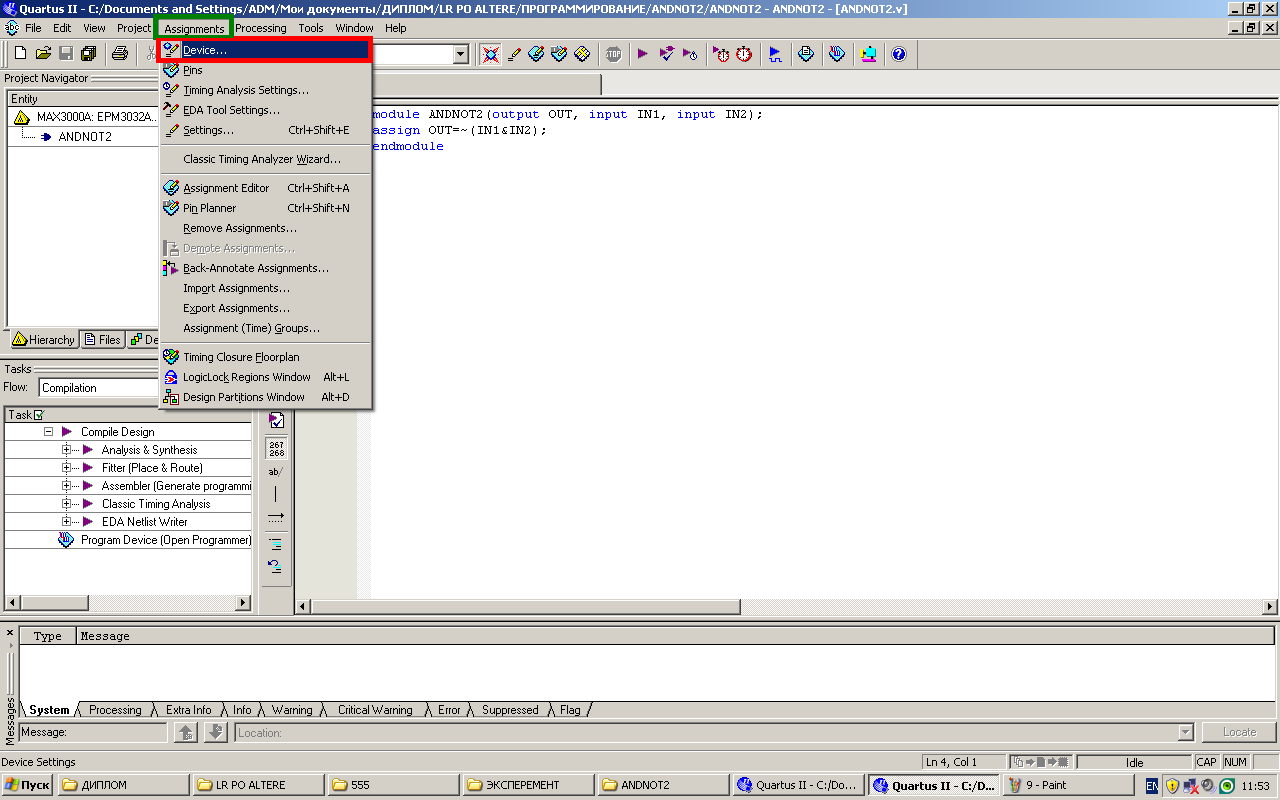

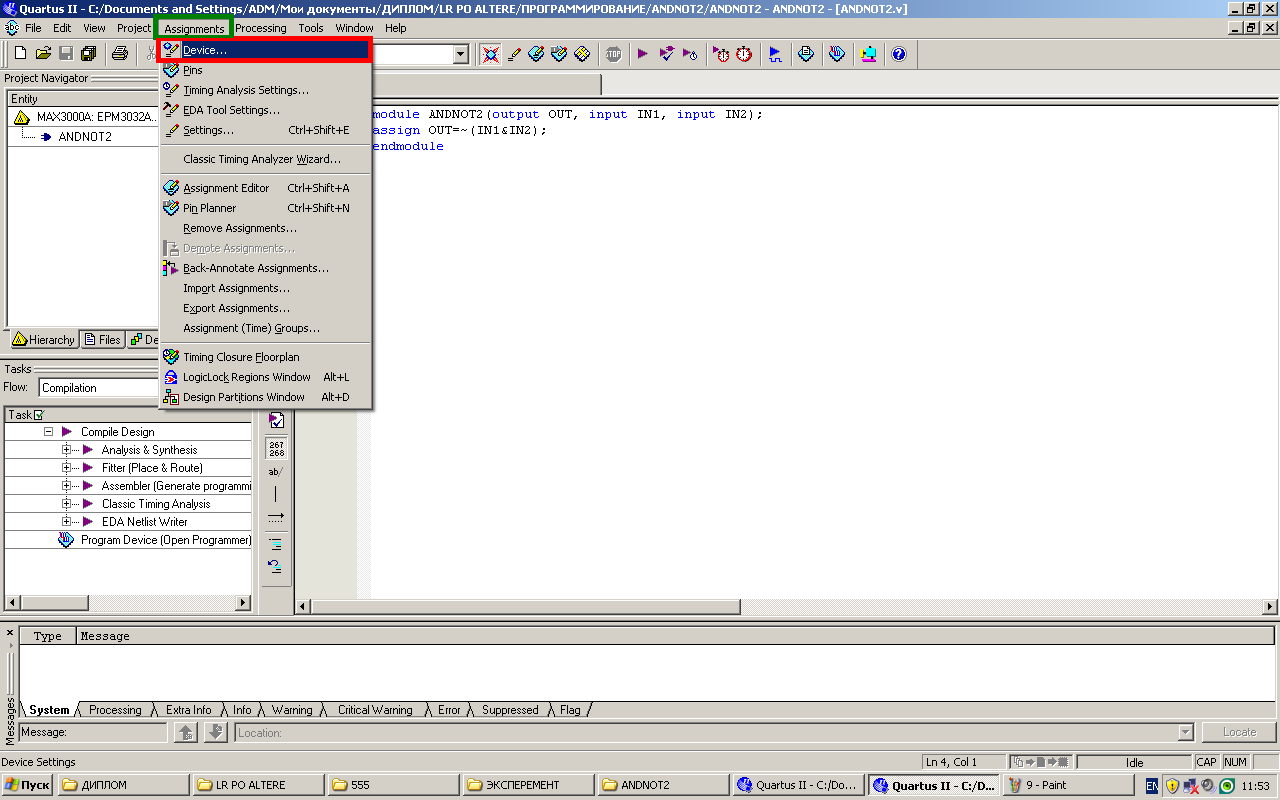

· Выбрать в главном меню "Assignments\Devise…" ("Назначения\Микросхема…") (рис. 2.40).

Рис. 2.40

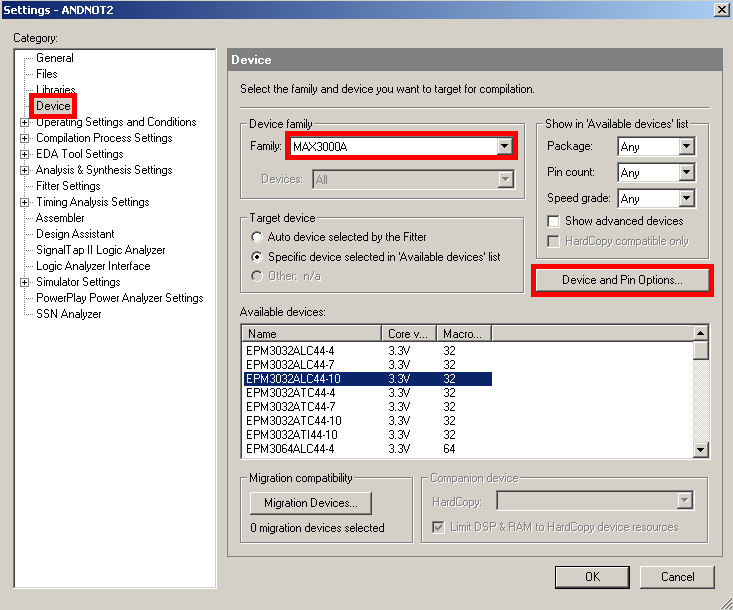

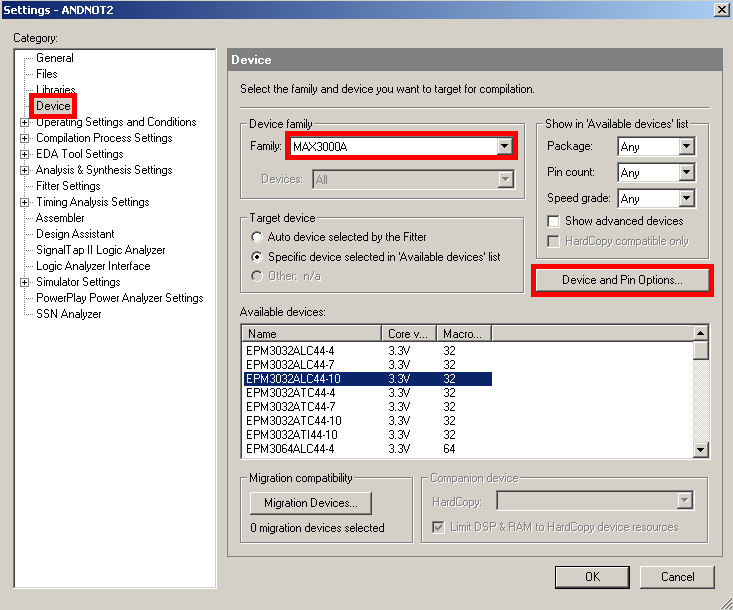

· В открывшемся окне "Devise " в списке "Familiy" ("Семейство") выбрать для нашего примера семейство микросхем MAX3000A. В расположенном ниже списке "Available devices:" ("Доступные микросхемы:") выбрать микросхему, например, EPM3032ALC44-10. Далее нажать на кнопку “Device and Pin Options “ (“устройство и варианты контактов”) (рис. 2.41).

Рис. 2.41

· В появившемся окне выбираем закладку “Unused Pins” (“неиспользованные контакты”) и в графе “Reserve all unused pins” (“Для всех неиспользованных контактов ”) выбрать “As input tri-started” (“В качестве входов с высоким входным сопротивлением”) (рис. 2.42). Это обозначает, что неиспользуемые входы будут входами с высоким входным сопротивлением. Это обезопасит микросхему и плату.

Рис. 2.42

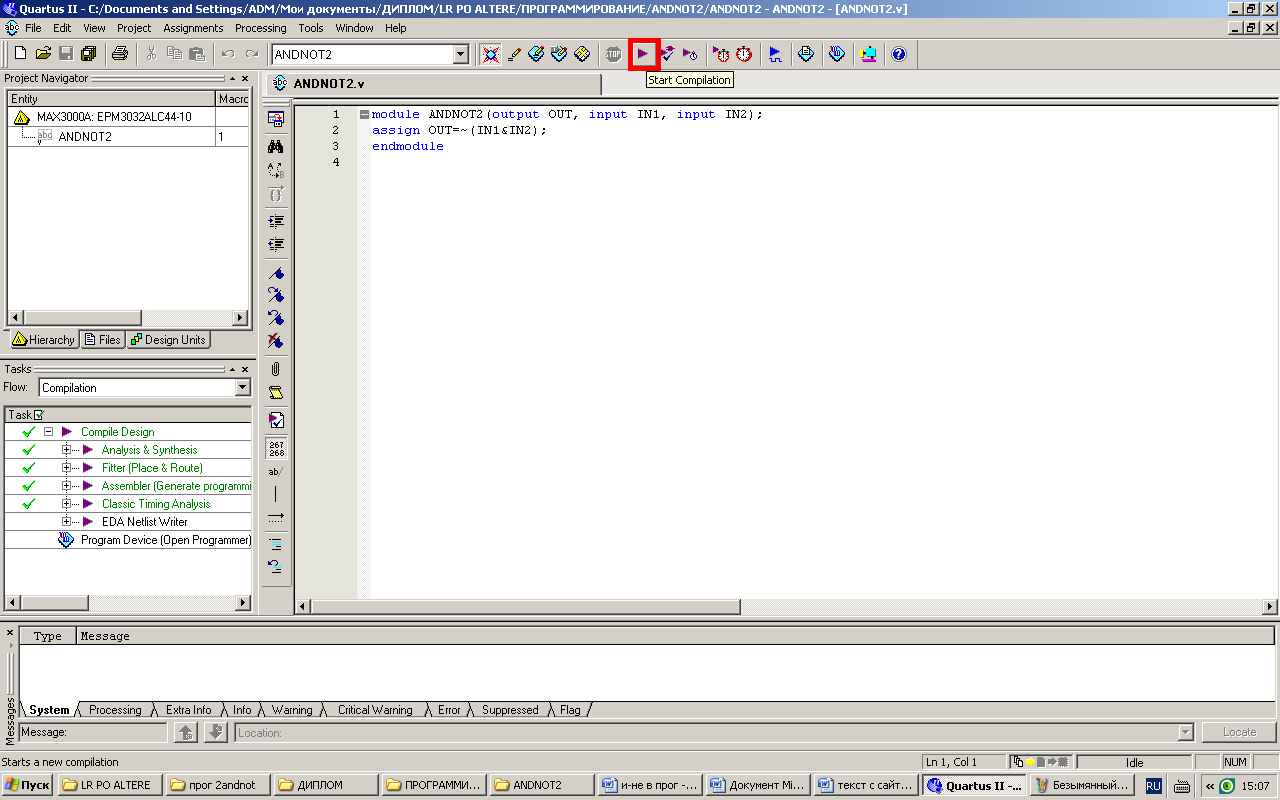

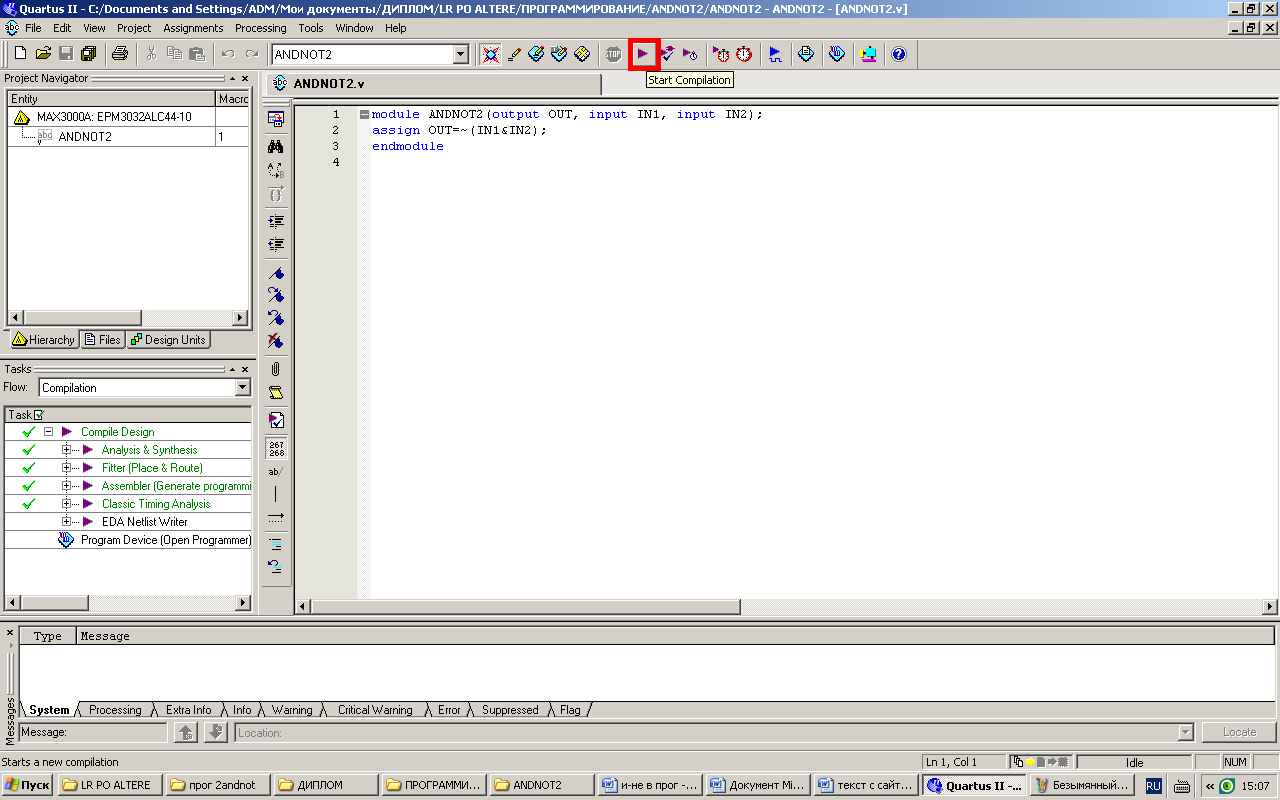

· Произвести компиляцию проекта, нажав на кнопку “Start Compilation”, находящейся на панели инструментов (рис. 2.43).

Рис. 2.43

· После компиляции должно выскочить сообщение о её успешном завершении.