Контроллер DMA используется для обмена данными между внешними устройствами и памятью. Он нужен в работе с жесткими дисками и дисководами, звуковыми платами и другими устройствами, работающими со значительными объемами данных. Начиная с PC AT, в компьютерах присутствуют два DMA-контроллера - 8-битный (с каналами 0,1,2 и 3) и 16-битный (с каналами 4, 5, 6 и 7). Канал 2 используется для обмена данными с дисководами, канал 3 - для жестких дисков, канал 4 теряется при каскадировании контроллеров, а назначение остальных каналов может варьироваться.

DMA позволяет выполнить чтение или запись блока данных, начинающегося с линейного адреса, который описывается как 20-битное число для первого DMA-контроллера и как 24-битное для второго, то есть данные для 8-битного DMA должны располагаться в пределах первого мегабайта памяти, а для второго - в пределах первых 16 Мб. Старшие четыре бита для 20-битных адресов и старшие 8 бит для 24-битных адресов хранятся в регистрах страниц DMA, адресуемых через порты 80h - 8Fh:

порт 81 h: страничный адрес для канала 2 (биты 3-0 = биты 19-16 адреса)

порт 82 h страничный адрес для канала 3 (биты 3-0 = биты 19-16 адреса)

порт 83 h: страничный адрес для канала 1 (биты 3-0 = биты 19-16 адреса)

порт 87 h: страничный адрес для канала 0 (биты 3-0 = биты 19-16 адреса)

порт 89 h: страничный адрес для канала 6 (биты 7-0 = биты 23-17 адреса)

порт 8А h: страничный адрес для канала 7 (биты 7-0 = биты 23-17 адреса)

порт 8 Bh: страничный адрес для канала 5 (биты 7-0 = биты 23-17 адреса)

Страничный адрес определяет начало 64/128-килобайтного участка памяти, с которым будет работать данный канал, поэтому при передаче данных через DMA обязательно надо следить за тем, чтобы не было выхода за границы этого участка, то есть чтобы не было попытки пересечения адреса 1000h:0, 2000h:0, 3000h:0 для первого DMA или 2000h:0, 4000h:0, 6000h:0 для второго.

Младшие 16 бит адреса записывают в следующие порты:

00h: биты 15-0 адреса блока данных для канала 0

01h: счетчик переданных байт канала 0

02h - 03 h: аналогично для канала 1

04h - 05h: аналогично для канала 2

06h - 07h: аналогично для канала 3

(для этих портов используются две операции чтения/записи - сначала передаются

биты 7-0, затем биты 15-8)

0C0h: биты 8-1 адреса блока данных для канала 4 (бит 0 адреса всегда равен нулю)

0C1h: биты 16-9 адреса блока данных для канала4

0С2 h: младший байт счетчика переданных слов канала 4

0C3h: старший байт счетчика переданных слов канала 4

0C4h - 0C7h: аналогично для канала 5

0C8h - 0CBh: аналогично для канала 5

0CCh - 0CFh: аналогично для канала 5

(эти порты рассчитаны на чтение/запись целыми словами)

Каждый из указанных двух DMА-контроллеров также имеет собственный набор управляющих регистров - регистры первого контроллера адресуются через порты 08h - 0Fh, а второго - через 0D0 - 0DFh:

порт 08 h /0 D 0 h для чтения: регистр состояния DMA

бит 7, 6,5, 4: установлен запрос на DMA на канале 3/7, 2/6,1/5,0/4

бит 3, 2, 1, 0; закончился DMA на канале 3/7, 2/6, 1/5, 0/4

порт 08 h / D 0 h для записи: регистр команд DMA (устанавливается BIOS)

бит 7: сигнал DACK использует высокий уровень

бит 6: сигнал DREQ использует высокий уровень

бит 5: 1/0: расширенный/задержанный цикл записи

бит 4: 1/0: приоритеты сменяются циклически/фиксировано

бит 3: сжатие во времени

бит 2: DMА-контроллер отключен

бит 1: разрешен захват канала 0 (для режима память-память)

бит 0: включен режим память-память (канал 0 - канал 1)

порт O 9 h /0 D 2 h для записи: регистр запроса DMA

бит 2: 1/0: установка/сброс запроса на DMA

биты 1-0: номер канала (00, 01, 10,11 - 0/4, 1/5, 2/6, 3/7)

порт 0 Ah /0 D 4 h для записи: регистр маски канала DMA

бит 2: 1/0: установка/сброс маскирующего бита

биты 1-0: номер канала (00,01, 10, И -0/4, 1/5,2/6,3/7)

порт 0 Bh / OD 6 h для записи: регистр режима DMA

биты 7-6:

00 - передача по запросу

01 - одиночная передача (используется для звука)

10 - блочная передача (используется для дисков)

11 - канал занят для каскадирования

бит 5: 1/0: адреса уменьшаются/увеличиваются

бит 4: режим автоинициализации

биты 3-2:

00 - проверка

01 - запись

10 - чтение

биты 1-0: номер канала (00, 01, 10, 11 - 0/4, 1/5, 2/6, 3/7)

порт 0 Ch /0 D 8 k для записи: сброс переключателя младший/старший байт

Для чтения/записи 16-биткых значений из/в 8-битные порты 00h-08h. Очередной байт, переданный в эти порты, будет считаться младшим, а следующий за ним - старшим.

порт 0 Dh /0 DAh для записи: сброс контроллера DMA

Любая запись сюда приводит к полному сбросу DMA-контроллера, так что его надо инициализировать заново.

порт 0 Dh /0 DAh для чтения: последний переданный байт/слово.

порт 0 Eh /0 DCh для записи: любая запись снимает маскирующие биты со всех каналов

порт 0 Fh /0 DEh для записи: регистр маски всех каналов:

биты 3-0: маскирующие биты каналов 3/7, 2/6, 1/5, 0/4

Чаще всего внешнее устройство само инициализирует передачу данных, и все, что необходимо сделать программе, - это записать адрес начала буфера в порты, соответствующие используемому каналу, длину передаваемого блока данных минус один в регистр счетчика нужного канала, установить режим работы канала и снять маскирующий бит.

Описание функции Open_file

open_file proc near

mov ax,3D00h;Выполнить функцию DOS 3 Dh: AH=3Dh,установим

режим доступа AL=00 – открыть для чтения

mov dx,offset filename;Заносим в dx смещение filename и

теперь в DS:DX –полный адрес ASCIZ-

строки с именем файла

int 21h;Передать управление операц. системе и открыть

файл для чтения

jc error_exit; если не удалось открыть файл,перейти на

метку error_exit

mov bx,ax; заносим идентификатор файла в BX,

необходимо для команды 42h

mov ax,4200h;Команда для перемещения указателя чтения/записи AH=42h,

AL=0 – от начала файла

mov cx,0; CX:DX - новое значение указателя

mov dx,38h; по этому адресу начинаются данные в tada.wav

int 21h; переместим файловый указатель

mov ah,3Fh ; Чтение из файла AH=3Fh

mov cx,27459; считать 27459 байтов в файле tada.wav

push ds ;заносим считанные данные в стек

mov dx,ds

and dx,0F000h; выровняем буфер на границу 4K-страницы

add dx,1000h; складываем dx и 1000h, необход. для DMA

mov ds,dx

mov dx,0; DS:DX - адрес буфера

int 21h; чтение файла

pop ds ; выгрузить из стека данные в ds

ret

error_exit: ; если не удалось открыть файл

mov ah,9; AH=09h

mov dx,offset notopenmsg; DS:DX = адрес сообщения об

; ошибке

int 21h; вывод строки на экран

int 20h; конец программы

notopenmsg db 'Could not open file',0Dh,0Ah; сообщение об

; ошибке

db 'Exiting',0Dh,0Ah,'$'

open_file endp

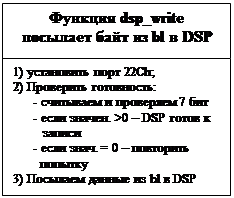

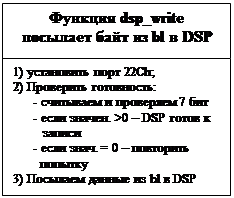

Алгоритм и блок-схема

Алгоритм и блок-схема

| Считываем данные из файла

| |

Компиляция

Для компиляции будем использовать компилятор и линковщик Tasm и Tlink соответственно:

tasm /m wavdma.asm

tlink /t /x wavdma.obj

Алгоритм и блок-схема

Алгоритм и блок-схема